## LIGO Laboratory / LIGO Scientific Collaboration

| LIGO- T0900291                         | Advanced LIGO UK | December 2009 |

|----------------------------------------|------------------|---------------|

| PUM Driver Board Test Report           |                  |               |

| R. M. Cutler, University of Birmingham |                  |               |

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

Institute for Gravitational Research University of Glasgow Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833 E-mail <u>k.strain@physics.gla.ac.uk</u> Engineering Department CCLRC Rutherford Appleton Laboratory Phone +44 (0) 1235 445 297 Fax +44 (0) 1235 445 843 E-mail J.Greenhalgh@rl.ac.uk School of Physics and Astronomy University of Birmingham Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail <u>av@star.sr.bham.ac.uk</u> Department of Physics University of Strathclyde Phone +44 (0) 1411 548 3360 Fax +44 (0) 1411 552 2891 E-mail <u>N.Lockerbie@phys.strath.ac.uk</u>

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

## Contents

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Monitor Outputs

- 8.1 Amplifier Monitors 8.2 Coil Monitors

- 9. Filter Frequency Response Test

- 10. Distortion

- **11. Trip Circuit tests**

- 12 Load Tests 12.1 Noisy Mode 12.2 Low noise Mode 12.3 Acquisition Mode

13. DC Stability

## 1. Description

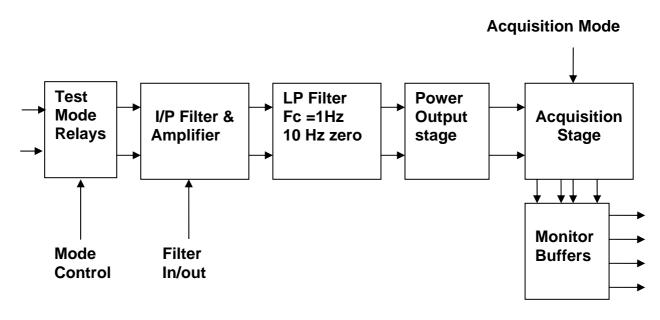

## **Block diagram**

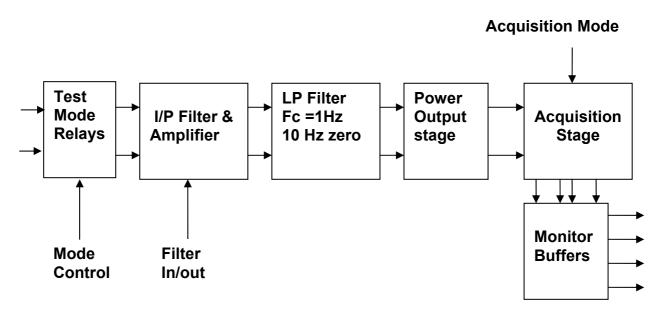

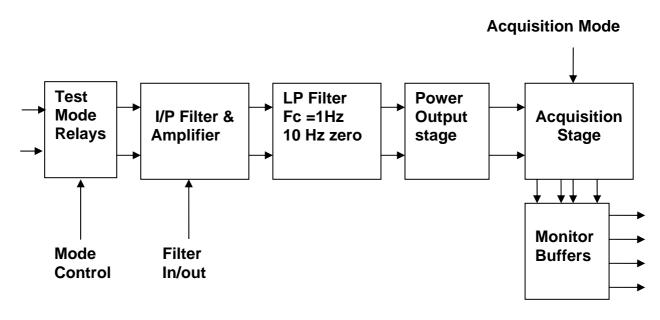

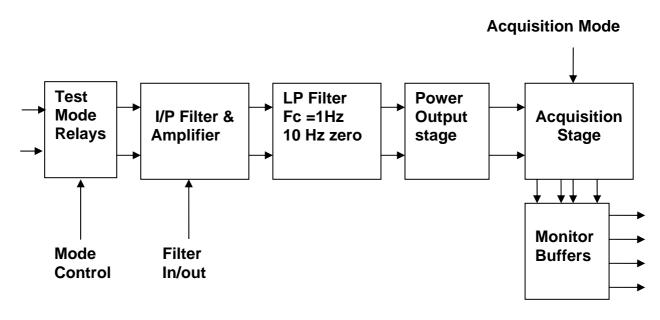

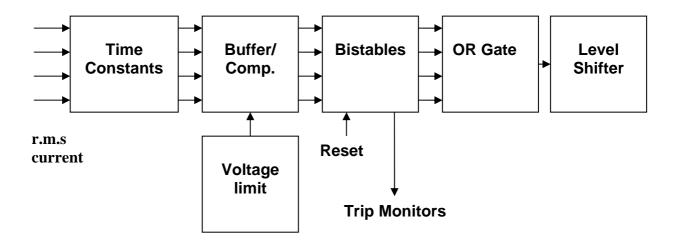

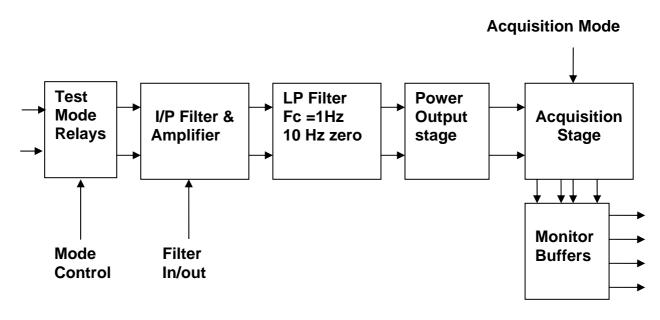

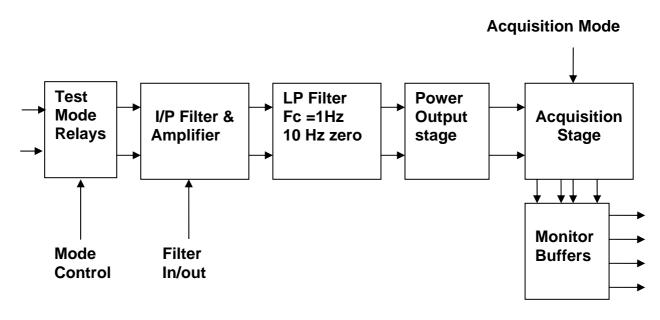

#### Description

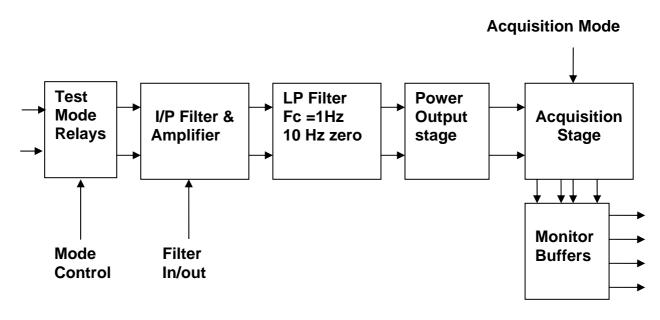

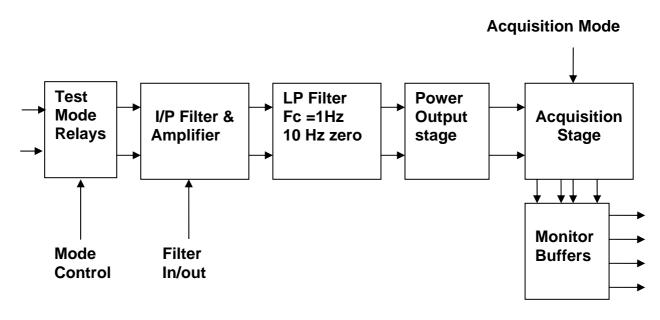

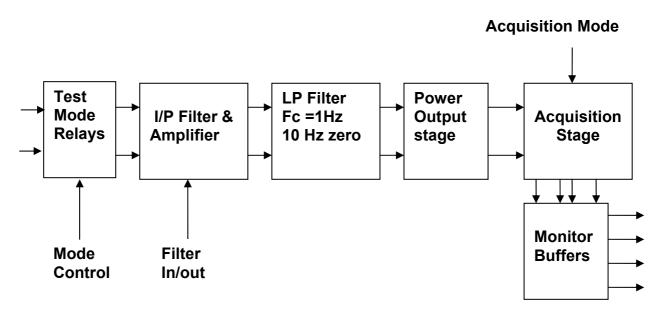

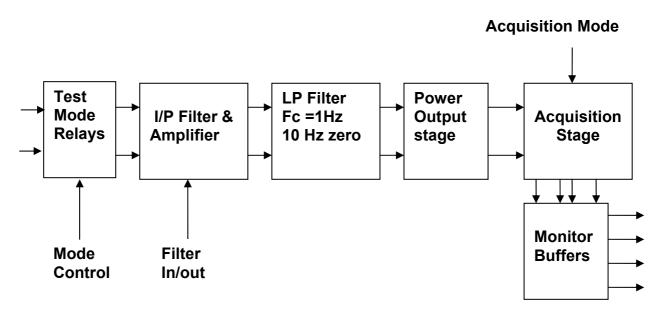

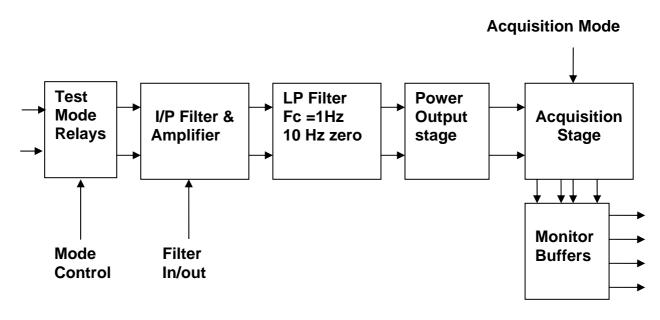

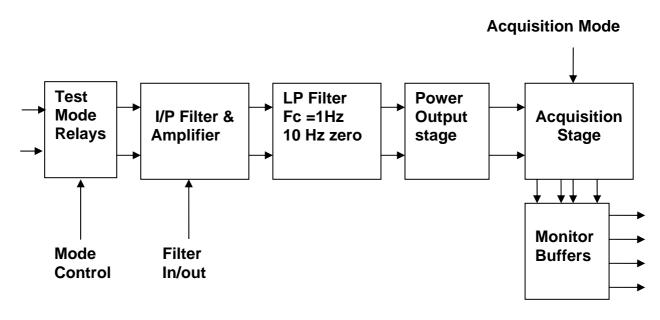

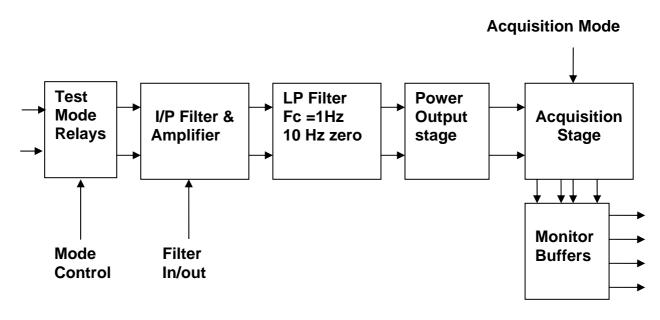

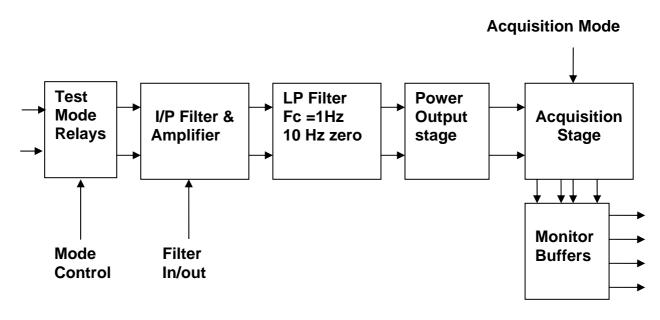

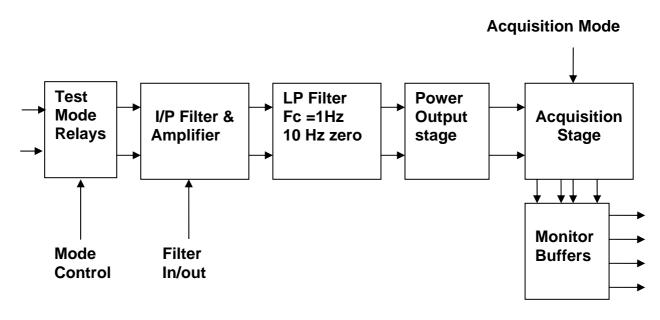

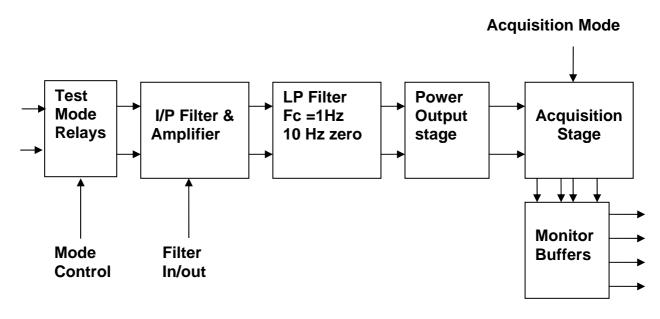

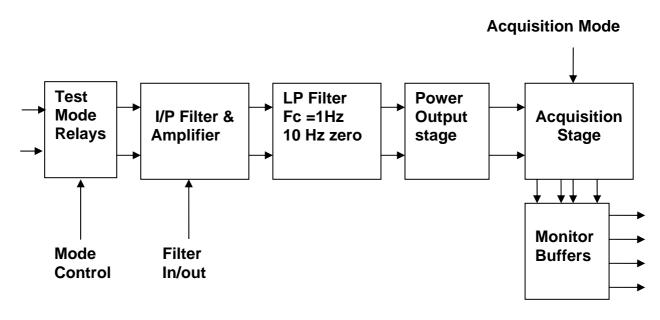

Each PUM Driver board consists of four identical channels and the power regulators which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block has a gain of 1.2.

The third block contains a low pass filter with a corner frequency of 0.5 Hz, followed by a complimentary zero at 5 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 0.5 Hz, the attenuation increases at a rate of 10dB/decade up to the corner frequency of the zero at 5 Hz, after which the characteristic levels off. This filter may be switched in and out by command as required under relay control.

The third block also contains a high pass section which increases the gain at high frequencies to give the required dynamic range at high frequencies.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is wired to have unity gain, the operational amplifier providing the internal gain in the loop. The loop is closed around the buffer/operational amplifier pair. The current limit is set of the driver is set to 0. 5A

The current limit during acquisition is controlled by a circuit which is common to all driver channels (described below).

The outputs are buffered by unity gain voltage followers which drive the monitor board.

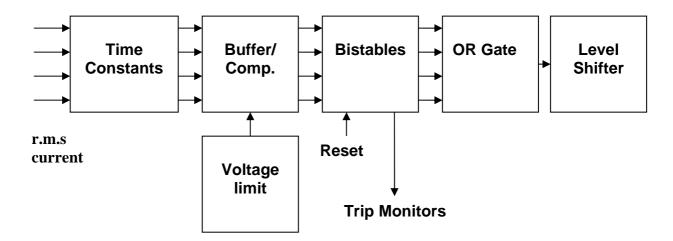

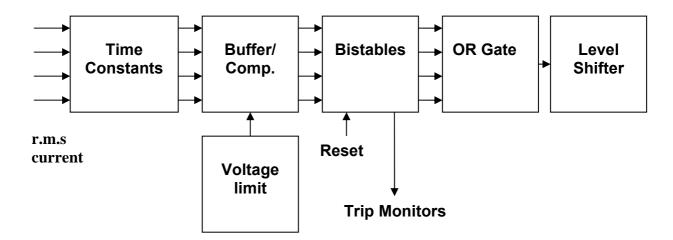

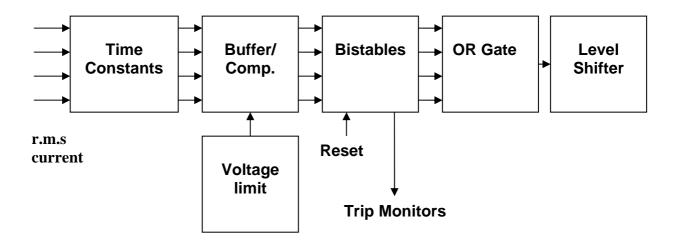

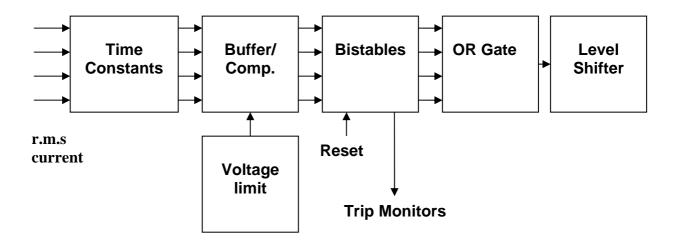

## **Acquisition Mode Current Limit**

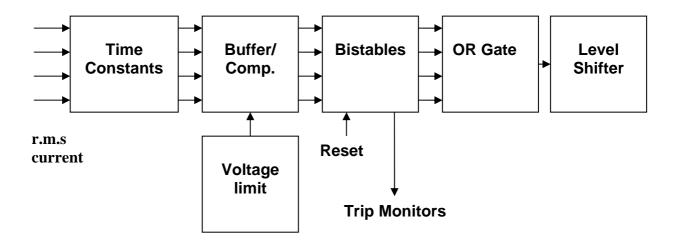

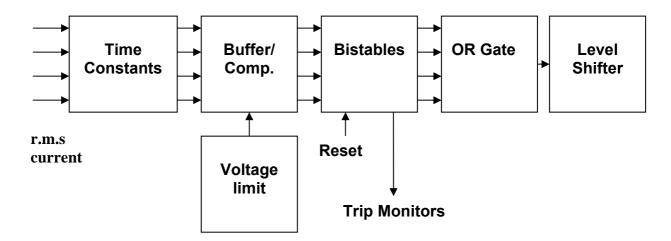

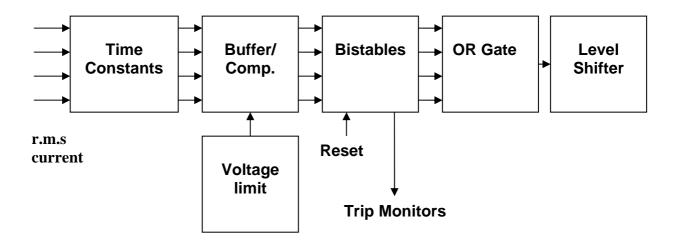

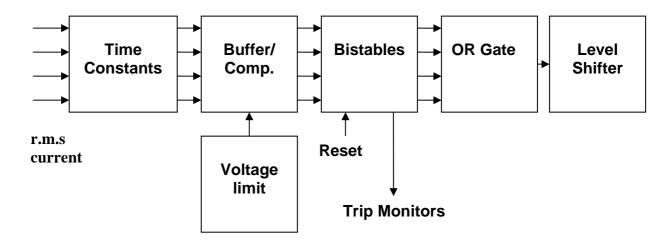

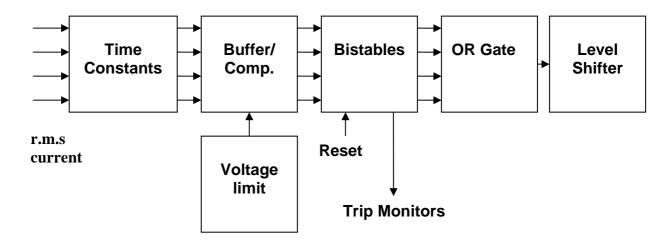

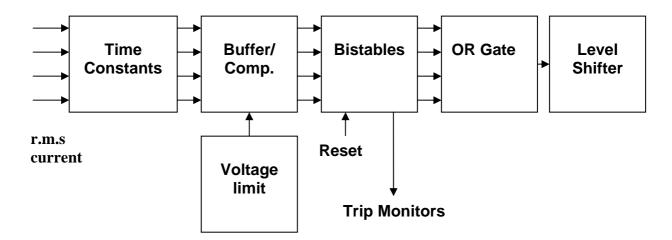

The current limit during acquisition mode is controlled by an OSEM protection circuit which is common to all channels.

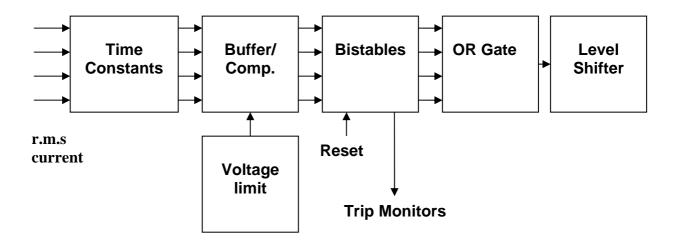

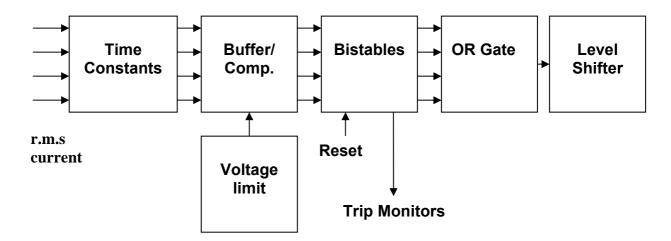

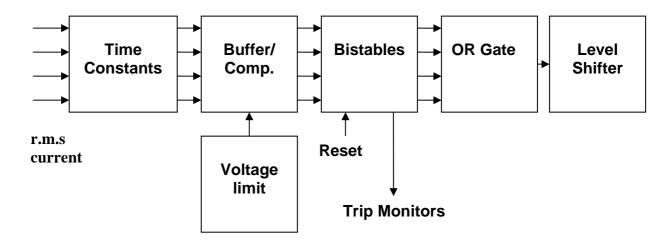

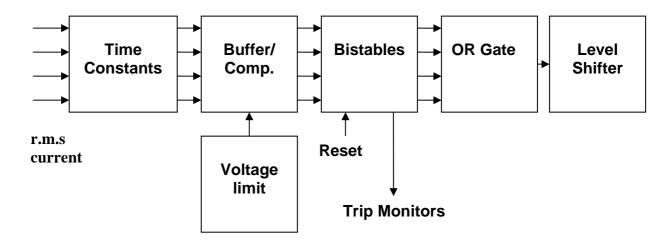

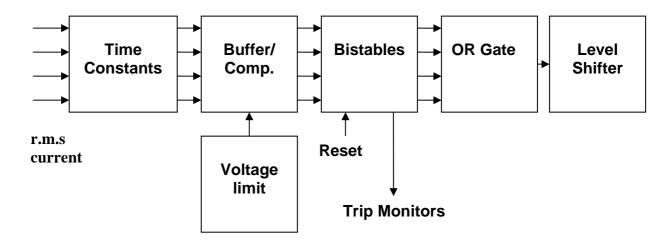

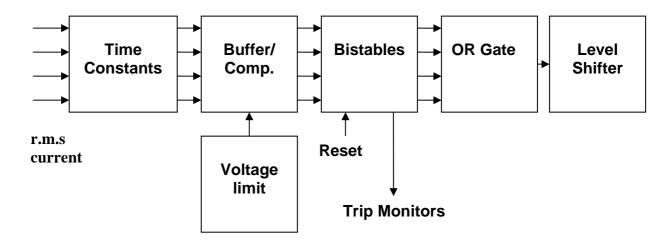

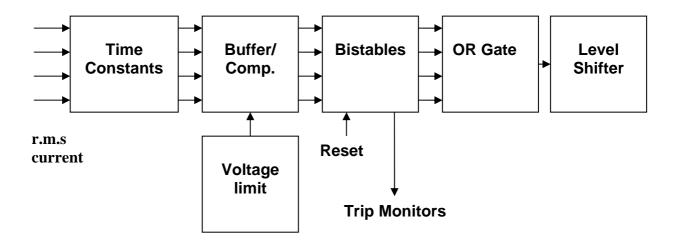

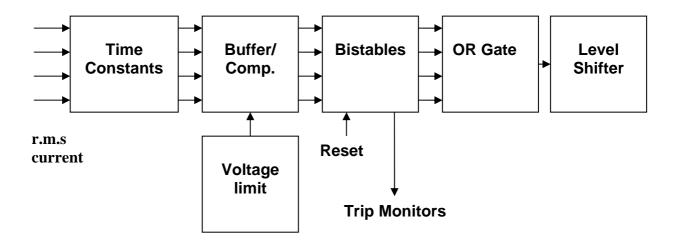

The RMS output currents are measured on the monitor board, then fed into the OSEM Protection Circuit. This circuit is designed to trip if the r.m.s current into an OSEM exceeds the preset limit for more than a predetermined time.

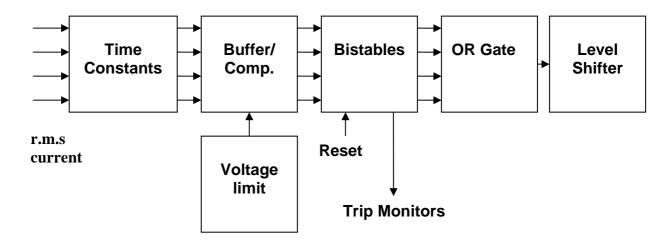

## The OSEM Protection Circuit

The OSEM coils must not be allowed to overheat, as this causes out-gassing. However, during Acquisition, a high current is required for a short period. This period is not long enough to allow the coil to become hot and outgas significantly. However the coils require protection against excessive currents for prolonged periods.

The inputs to the OSEM protection circuit monitor the r.m.s current flowing in each Osem coil. A voltage proportional to the r.m.s current is passed through a delay network. If an OSEM current exceeds the limit by more than a certain time, the threshold level is reached, and the corresponding bistable is set.

The outputs of the four bistables are combined in an OR gated, energising a level shifting circuit which switches off all the drivers. The use of a bistable ensures that oscillation is prevented.

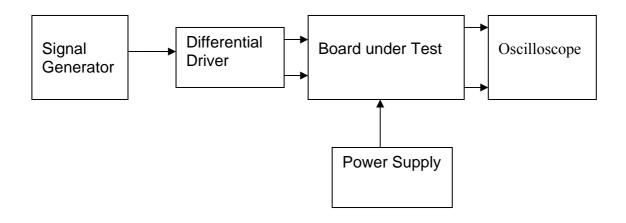

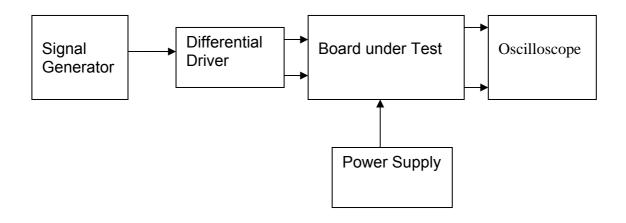

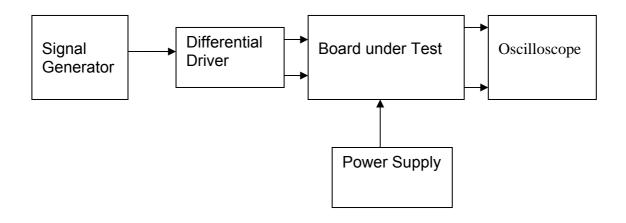

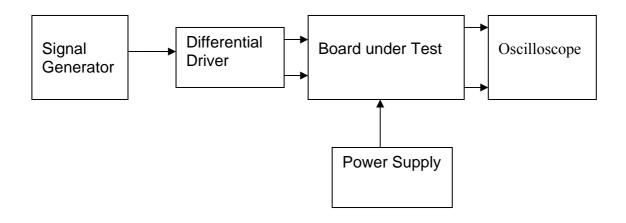

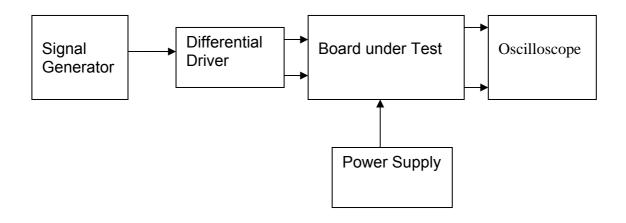

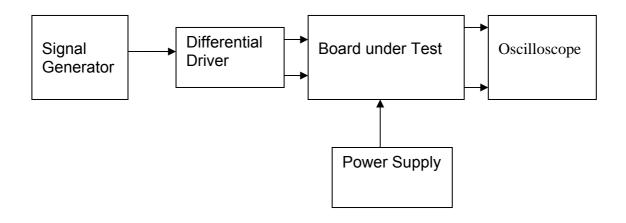

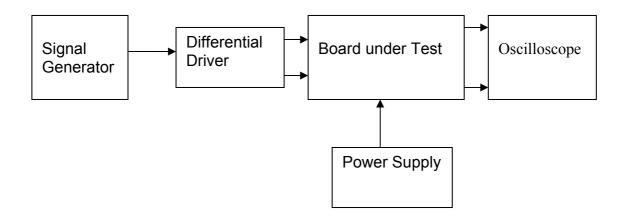

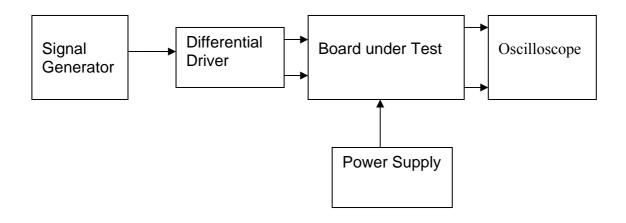

## 2. Test equipment

Power supplies (At least +/- 20v variable, 1A) Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz)) Digital oscilloscope Analogue oscilloscope Agilent Dynamic Signal Analyser (or similar) Low noise Balanced Driver circuit Relay test box

Record the Models and serial numbers of the test equipment used below.

| DVM                | Fluke     | 287   |

|--------------------|-----------|-------|

| Voltage calibrator | Time      | 1044  |

| PSU                | Farnell   | 30-2  |

| PSU                | Farnell   | 30-2  |

| Scope              | Tektronix | 2225  |

| DSA                | Agilent   | 35670 |

| Precision Amp      | Stanford  | SR560 |

## 3. Inspection

#### Workmanship

Inspect the general workmanship standard and comment:

## Ok

**Reset link in place (J7/2 to 18)**

Solder joint on C1, channel 4 reworked because of a dry joint.

Links:

Check that the link W4 is present on each channel.

Connect the test lead to ground pins 1, 3, 5 and 7 on P3, the Monitor Input 16 way header.

# 4. Continuity Checks

J2

| PIN | SIGNAL | DESCRIPTION   | To J1 PIN | OK?          |

|-----|--------|---------------|-----------|--------------|

| 1   | PD1P   | Photodiode A+ | 1         |              |

| 2   | PD2P   | Photodiode B+ | 2         | $\checkmark$ |

| 3   | PD3P   | Photodiode C+ | 3         | $\checkmark$ |

| 4   | PD4P   | Photodiode D+ | 4         | $\checkmark$ |

| 5   | 0V     |               |           |              |

| 6   | PD1N   | Photodiode A- | 14        | $\checkmark$ |

| 7   | PD2N   | Photodiode B- | 15        | $\checkmark$ |

| 8   | PD3N   | Photodiode C- | 16        | $\checkmark$ |

| 9   | PD4N   | Photodiode D- | 17        |              |

## J5

| PIN | SIGNAL | To J1 | PIN OK?      |

|-----|--------|-------|--------------|

| 1   | Imon1P | 5     |              |

| 2   | Imon2P | 6     |              |

| 3   | Imon3P | 7     | $\checkmark$ |

| 4   | Imon4P | 8     |              |

| 5   | 0V     |       |              |

| 6   | Imon1N | 18    | $\checkmark$ |

| 7   | Imon2N | 19    |              |

| 8   | Imon3N | 20    | $\checkmark$ |

| 9   | Imon4N | 21    | $\checkmark$ |

# Power Supply to Satellite box

J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | $\checkmark$ |

| 10  | V+ (TP1) | +17v Supply | $\checkmark$ |

| 11  | V- (TP2) | -17v Supply | $\checkmark$ |

| 12  | V- (TP2) | -17v Supply | $\checkmark$ |

| 13  | 0V (TP3) |             | $\checkmark$ |

| 22  | 0V (TP3) |             | $\checkmark$ |

| 23  | 0V (TP3) |             | $\checkmark$ |

| 24  | 0V (TP3) |             | $\checkmark$ |

| 25  | 0V (TP3) |             | $\checkmark$ |

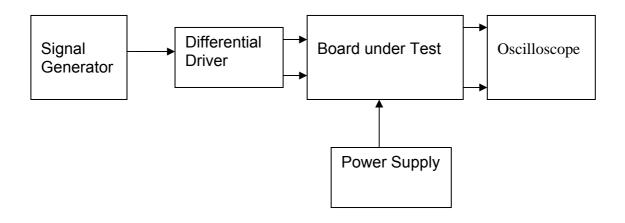

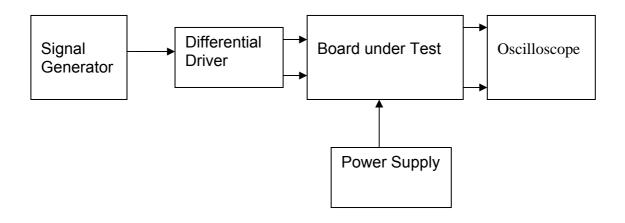

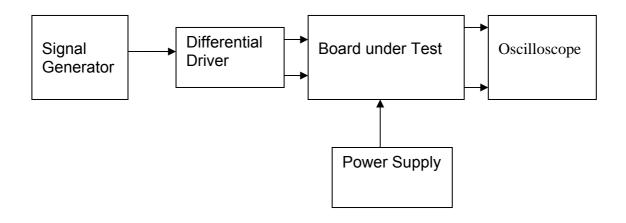

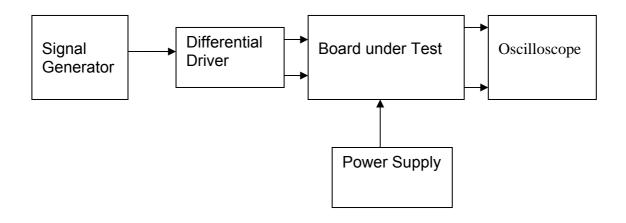

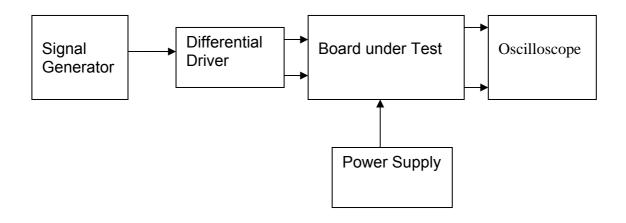

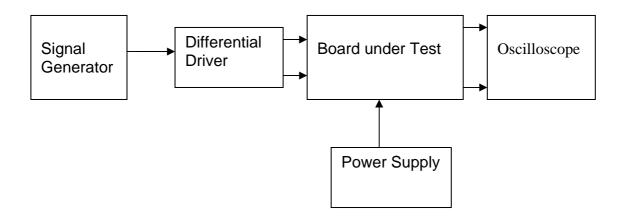

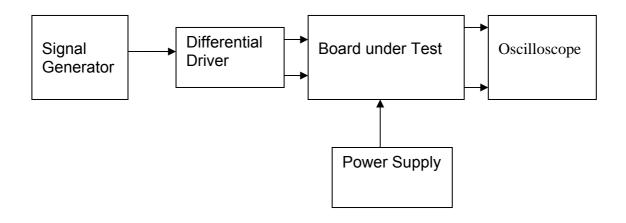

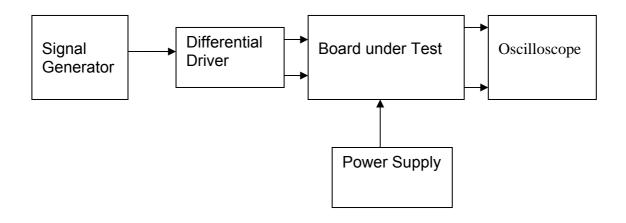

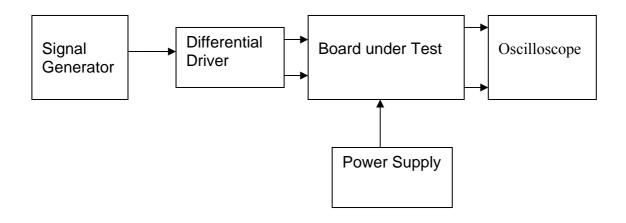

## 5. TEST SET UP

Note:

(1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

(2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

## **Connections:**

#### Differential signal inputs to the board under test:

J3 pins 1, 2, 3, 4 = positive input J3 pins 6, 7, 8, 9 = negative input J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v J1 pin 11,12 = -16.5 J1 pins 22, 23, 24, 25 = 0v

#### **Outputs**

| Ch1+ = J4 pin 1 | Ch1- = J4 pin 9  |

|-----------------|------------------|

| Ch2+ = J4 pin 3 | Ch2- = J4 pin 11 |

| Ch3+ = J4 pin 5 | Ch3- = J4 pin 13 |

| Ch4+ = J4 pin 7 | Ch4- = J4 pin 15 |

## 6. Power

# Check that the 3 pin power connector is wired correctly: A1 positive, A2 return, A3 Negative.

Set the power supply outputs to zero.

Connect power to the unit

Ensure that the test ribbon cable is connected to P3, and that pins 1,3,5 and 7 are grounded.

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Press the reset button on the test box.

Record the output voltages, measured on a DVM with 4 or more digits, from each regulator

Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each regulator output.

Record regulator outputs:

| Regulator | Output voltage | Nominal +/-<br>0.5v? | Output noise |

|-----------|----------------|----------------------|--------------|

| +12v TP5  | +12.017        | $\checkmark$         | 2mV          |

| +15v TP4  | -15.040        | $\checkmark$         | 1.5 mV       |

| -15v TP6  | +14.876        | $\checkmark$         | 7 mV         |

| All Outputs smooth DC, no oscillation? | N |  |

|----------------------------------------|---|--|

|                                        | v |  |

## Some pick up present

## **Record Power Supply Currents**

| Supply | Current |

|--------|---------|

| +16.5v | 0.294 A |

| -16.5v | 0.232 A |

If the supplies are correct, proceed to the next test.

## 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

#### Filter

| Channel | Indicat      | Indicator    |              |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ |              | $\checkmark$ |

| Ch3     | $\checkmark$ |              | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

## **TEST RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     |              |              | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ |              | $\checkmark$ |

| Ch4     | $\checkmark$ |              | $\checkmark$ |

## **ACQUISITION RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ |              |

| Ch3     |              | $\checkmark$ |              |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

Press the Reset button on the test box. Ensure that the "Not Tripped" indicators are on.

## **NOT TRIPPED indicators**

| Channel | Indicator    |

|---------|--------------|

|         | ON?          |

| Ch1     | $\checkmark$ |

| Ch2     | $\checkmark$ |

| Ch3     | $\checkmark$ |

| Ch4     | $\checkmark$ |

## 8. Monitor Outputs

Switch out the filters and set the unit to Acquisition Mode.

With a 20 ohm dummy load on each channel, apply a 1v r.m.s input at 100Hz as measured between TP1 and TP2. Measure the voltage monitor outputs and compare with the voltages between TP10 and TP12.

Measure the current monitor outputs and compare with the voltage between the outputs of R29 and R130. Repeat for each channel.

A ribbon cable grounding pins 1, 3, 5 and 7 is necessary in the r.m.s header socket. Press the Reset button on the test box.

Ensure that the "Not Tripped" lights are on.

## 8.1 Voltage Monitors

| Ch. | Output:<br>TP10 to TP12 |                  |       | Pass/Fail:<br>Equal? (+/- 0.1v) |

|-----|-------------------------|------------------|-------|---------------------------------|

| 1   | 1.201                   | Pin 1 to Pin 2   | 1.201 |                                 |

| 2   | 1.201                   | Pin 5 to Pin 6   | 1.200 |                                 |

| 3   | 1.200                   | Pin 9 to Pin 10  | 1.200 |                                 |

| 4   | 1.201                   | Pin 13 to Pin 14 | 1.200 |                                 |

## 8.2 Current monitors

| Ch. | Output<br>between R29<br>and R130 | Monitor Pins     | Monitor<br>Voltage | Pass/Fail:<br>Equal? (+/- 0.1v) |

|-----|-----------------------------------|------------------|--------------------|---------------------------------|

| 1   | 0.962                             | Pin 3 to Pin 4   | 0.962              | $\checkmark$                    |

| 2   | 0.964                             | Pin 7 to Pin 8   | 0.964              | $\checkmark$                    |

| 3   | 0.964                             | Pin 11 to Pin 12 | 0.964              | $\checkmark$                    |

| 4   | 0.967                             | Pin 15 to Pin 16 | 0.967              |                                 |

**9.** Frequency Response Test, Low Noise Mode: Insert link W4 for each channel. Switch in the filter and test the response using the signal generator. With a 1Vrms input signal between TP1 and TP2, measure the output between TP10 and TP12. Alternatively, use the Dynamic Signal analyser.

#### 0.1Hz

|     | Output | -6dB | Simulation  |              | Pass/Fail    |

|-----|--------|------|-------------|--------------|--------------|

| Ch1 | 1.23   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch2 | 1.13   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch3 | 1.20   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch4 | 1.27   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

#### 1Hz

|     | Output | -6dB | Simulation   |                | Pass/Fail    |

|-----|--------|------|--------------|----------------|--------------|

| Ch1 | 0.53   |      | 0.48 to 0.6v | -6.5 to -4.5dB |              |

| Ch2 | 0.54   |      | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

| Ch3 | 0.53   |      | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

| Ch4 | 0.50   |      | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

#### 10Hz

|     | Output | -6dB | Simulation    |                  | Pass/Fail    |

|-----|--------|------|---------------|------------------|--------------|

| Ch1 | 0.13   |      | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch2 | 0.13   |      | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch3 | 0.13   |      | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch4 | 0.13   |      | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

#### 100Hz

|     | Output | -6dB | Simulation    |                | Pass/Fail    |

|-----|--------|------|---------------|----------------|--------------|

| Ch1 | 0.472  |      | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch2 | 0.476  |      | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch3 | 0.469  |      | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch4 | 0.465  |      | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

#### 1 KHz

|     | Output | -6dB | Simulation   |                | Pass/Fail    |

|-----|--------|------|--------------|----------------|--------------|

| Ch1 | 1.16   |      | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch2 | 1.16   |      | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch3 | 1.16   |      | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch4 | 1.16   |      | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

|     | Output | -6dB | Simulation  |              | Pass/Fail    |

|-----|--------|------|-------------|--------------|--------------|

| Ch1 | 1.18   |      | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch2 | 1.18   |      | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch3 | 1.18   |      | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch4 | 1.18   |      | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

**10.** Frequency Response Test, Acquisition Mode: Switch the filter off and Acquisition mode on. Connect a 20 ohm load resistor each channel. Test the response using the signal generator. With a 1v rms input signal between TP1 and TP2, measure the output across the load resistor.

#### 0.1Hz

|     | Output | -6dB | Simulation   |                | Pass/Fail |

|-----|--------|------|--------------|----------------|-----------|

| Ch1 | 5 mV   |      | 0.3 to 0.4mV | -70dB to -65dB |           |

| Ch2 | 5.3 mV |      | 0.3 to 0.4mV | -70dB to -65dB |           |

| Ch3 | 5.3 mV |      | 0.3 to 0.4mV | -70dB to -65dB |           |

| Ch4 | 5 mV   |      | 0.3 to 0.4mV | -70dB to -65dB |           |

#### 1Hz

|     | Output | -6dB | Simulation   |                | Pass/Fail |

|-----|--------|------|--------------|----------------|-----------|

| Ch1 | 5 mV   |      | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch2 | 5 mV   |      | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch3 | 5 mV   |      | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch4 | 5 mV   |      | 3.3 to 4.2mV | -50dB to -45dB |           |

#### 10Hz

|     | Output | -6dB | Simulation |                | Pass/Fail    |

|-----|--------|------|------------|----------------|--------------|

| Ch1 | 40mV   |      | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch2 | 40mV   |      | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch3 | 39mV   |      | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch4 | 39 mV  |      | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

#### 100Hz

|     | Output | -6dB | Sim            | ulation       | Pass/Fail    |

|-----|--------|------|----------------|---------------|--------------|

| Ch1 | 0.294  |      | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch2 | 0.294  |      | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch3 | 0.294  |      | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch4 | 0.291  |      | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

#### 1 KHz

|     | Output | -6dB | Sim           | ulation      | Pass/Fail    |

|-----|--------|------|---------------|--------------|--------------|

| Ch1 | 0.471  |      | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch2 | 0.473  |      | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch3 | 0.471  |      | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch4 | 0.472  |      | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

|     | Output | -6dB | Sim           | ulation      | Pass/Fail    |

|-----|--------|------|---------------|--------------|--------------|

| Ch1 | 0.472  |      | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch2 | 0.473  |      | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch3 | 0.471  |      | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch4 | 0.473  |      | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

## **11. Distortion**

Switch the filters out. Increase input voltage to 10v peak, f = 1KHz. Use 20 Ohm loads. Observe the voltage across each load with an oscilloscope in both Acquisition and Non-Acquisition modes.

|     | Acquisition Mode:<br>Distortion Free? | Non-Acquisition Mode<br>Distortion Free? | ): |

|-----|---------------------------------------|------------------------------------------|----|

| Ch1 | $\checkmark$                          |                                          |    |

| Ch2 | $\checkmark$                          |                                          |    |

| Ch3 |                                       |                                          |    |

| Ch4 | $\checkmark$                          | $\checkmark$                             |    |

## **12. Trip Circuit Tests**

A test cable may be used for these tests, consisting of a ribbon cable which plugs into the 16 way header P3. It is convenient to common pins 1, 3, 5, 7, and apply a test voltage to them.

Alternatively an external test box may be used, enabling each input to be tested in turn.

Apply a test voltage to the inputs, and observe the OP400 outputs. An exponential rise in the outputs will be observed. When the logic threshold is reached, the bistable will become set, causing the OR gate output TP25 to go to logic 1. The collector of Q1 will go to high causing the trip pins on each of the drivers to be pulled down to the negative rail, switching them off,

Connect the test lead.

Observe TP25. It should initially be at 0v. If not, press the reset button on the test box or turn off all signal inputs and cycle the power supply.

Set the precision voltage source to 1v, representing an r.m.s current of 150mA, and connect it to the ribbon cable input. Observe TP25 for several minutes. It should not go high.

| Stays low? | Stays low? |  |

|------------|------------|--|

|------------|------------|--|

Very slowly increase the voltage, and observe the level at which it trips.

| Trip voltage? | 1.8 v |

|---------------|-------|

|---------------|-------|

Reduce the input voltage to 0v, and wait for the capacitors to discharge. Cycle the power supply.

Remove the voltage source, set it to 1.66v representing 250mA. Reconnect it, measuring how long it is before TP25 goes high.

| Time taken to trip? | 2.2 seconds |

|---------------------|-------------|

|---------------------|-------------|

Reduce the input voltage to 0v, and wait for the capacitors to discharge. Cycle the power supply.

Remove the voltage source, set it to 2.66v representing 400mA. Reconnect it, measuring how long it is before TP25 goes high.

| Time taken to trip? | 1.3 seconds |

|---------------------|-------------|

|---------------------|-------------|

## 12 Load tests

Plug in the 20 Ohm 5W loads. Ensure the links W4 are in place.

## 12.1 Noisy Mode

With the acquisition mode switched out, and filters switched out, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s meter, at the frequencies below.

Calculate the output current in each case (Vout/20).

#### 100Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) |

|-----|----------|------------------|

| Ch1 | 0.498    | 24.9 mA          |

| Ch2 | 0.495    | 24.7 mA          |

| Ch3 | 0.489    | 24.4 mA          |

| Ch4 | 0.494    | 24.7 mA          |

#### 200Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.655    | 32.7 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.654    | 32.7 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.650    | 32.5 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.654    | 32.7 mA          | >16mA         | $\checkmark$ |

#### 1 KHz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.750    | 37.5 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.750    | 37.5 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.749    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.751    | 37.5 mA          | >16mA         | $\checkmark$ |

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.749    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.750    | 37.5 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.749    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.751    | 37.5 mA          | >16mA         | $\checkmark$ |

## 12.2 Low noise Mode

With the acquisition mode switched out and filters switched in, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s, at the frequencies below. Calculate the output current in each case (Vout/20).

#### 100Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) |

|-----|----------|------------------|

| Ch1 | 0.195    | 9.75 mA          |

| Ch2 | 0.196    | 9.80 mA          |

| Ch3 | 0.190    | 9.50 mA          |

| Ch4 | 0.191    | 9.55 mA          |

#### 200Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.422    | 21.1 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.423    | 21.1 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.416    | 20.8 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.415    | 20.7 mA          | >16mA         |              |

#### 1 KHz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.729    | 36.4 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.730    | 36.5 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.728    | 36.4 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.729    | 36.4 mA          | >16mA         |              |

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.748    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch2 | 0.749    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch3 | 0.748    | 37.4 mA          | >16mA         | $\checkmark$ |

| Ch4 | 0.750    | 37.5 mA          | >16mA         | $\checkmark$ |

## **12.3 Acquisition Mode**

With the acquisition mode switched in, and filters switched out, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s meter at the frequencies below. Calculate the peak voltages, then the peak output current in each case (Vout/20). Do not leave the board running with a 10v input for long, especially if the heat sink is not fitted.

#### 100Hz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) |

|-----|----------|--------|----------------|

| Ch1 | 4.18     | 5.91   | 295 mA         |

| Ch2 | 4.18     | 5.91   | 295 mA         |

| Ch3 | 4.16     | 5.88   | 294 mA         |

| Ch4 | 4.15     | 5.87   | 293 mA         |

#### 200Hz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail |

|-----|----------|--------|----------------|---------------|-----------|

| Ch1 | 5.58     | 7.89   | 394 mA         | >400mA        |           |

| Ch2 | 5.59     | 7.90   | 395 mA         | >400mA        |           |

| Ch3 | 5.57     | 7.87   | 393 mA         | >400mA        |           |

| Ch4 | 5.56     | 7.86   | 393 mA         | >400mA        |           |

#### 1 KHz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail    |

|-----|----------|--------|----------------|---------------|--------------|

| Ch1 | 6.67     | 9.43   | 471 mA         | >400mA        | $\checkmark$ |

| Ch2 | 6.70     | 9.47   | 473 mA         | >400mA        | $\checkmark$ |

| Ch3 | 6.67     | 9.43   | 471 mA         | >400mA        | $\checkmark$ |

| Ch4 | 6.68     | 9.33   | 466 mA         | >400mA        | $\checkmark$ |

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail    |

|-----|----------|--------|----------------|---------------|--------------|

| Ch1 | 6.70     | 9.47   | 473 mA         | >400mA        | $\checkmark$ |

| Ch2 | 6.72     | 9.50   | 475 mA         | >400mA        | $\checkmark$ |

| Ch3 | 6.68     | 9.33   | 466 mA         | >400mA        | $\checkmark$ |

| Ch4 | 6.71     | 9.49   | 474 mA         | >400mA        | $\checkmark$ |

## 13. DC Stability

Use the precision voltage source via a break out box on the input (J3). All filters off. Check stability while slowly increasing the output voltage. (Link W2 in)

|      | Ch1<br>stable<br>? | Ch2<br>stable<br>? | Ch3<br>stable<br>? | Ch4<br>stable<br>? |

|------|--------------------|--------------------|--------------------|--------------------|

| -10v |                    | $\checkmark$       | $\checkmark$       | $\checkmark$       |

| -7v  |                    | $\checkmark$       |                    | $\checkmark$       |

| -5v  | $\checkmark$       | $\checkmark$       | $\checkmark$       | $\checkmark$       |

| -1v  |                    | $\checkmark$       |                    | $\checkmark$       |

| 0v   |                    | $\checkmark$       |                    | $\checkmark$       |

| 1v   |                    | $\checkmark$       |                    | $\checkmark$       |

| 5v   |                    | $\checkmark$       | $\checkmark$       | $\checkmark$       |

| 7v   |                    | $\checkmark$       |                    | $\checkmark$       |

| 10v  |                    | $\checkmark$       |                    | $\checkmark$       |

## LIGO Laboratory / LIGO Scientific Collaboration

| LIGO- T0900291                         | Advanced LIGO UK             | December 2009 |  |  |

|----------------------------------------|------------------------------|---------------|--|--|

|                                        | PUM Driver Board Test Report |               |  |  |

| R. M. Cutler, University of Birmingham |                              |               |  |  |

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

Institute for Gravitational Research University of Glasgow Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833 E-mail <u>k.strain@physics.gla.ac.uk</u> Engineering Department CCLRC Rutherford Appleton Laboratory Phone +44 (0) 1235 445 297 Fax +44 (0) 1235 445 843 E-mail J.Greenhalgh@rl.ac.uk School of Physics and Astronomy University of Birmingham Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail av@star.sr.bham.ac.uk Department of Physics University of Strathclyde Phone +44 (0) 1411 548 3360 Fax +44 (0) 1411 552 2891 E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm Unit......PUM2P......Serial No ..... Test Engineer ......RMC... Date ......4/1/2010

## Contents

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Monitor Outputs

- 8.1 Amplifier Monitors

- 8.2 Coil Monitors

- 9. Filter Frequency Response Test

- 10. Distortion

- 11. Trip Circuit tests

- 12 Load Tests 12.1 Noisy Mode 12.2 Low noise Mode 12.3 Acquisition Mode

13. DC Stability

## 1. Description

## **Block diagram**

#### Description

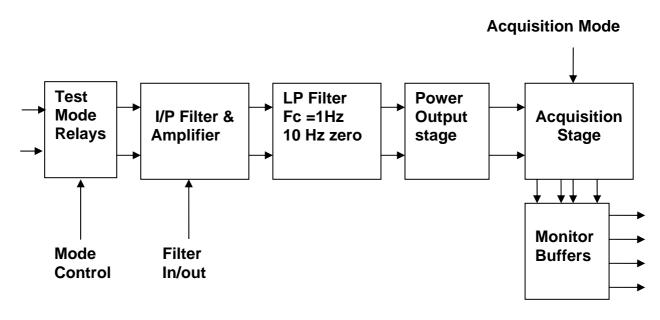

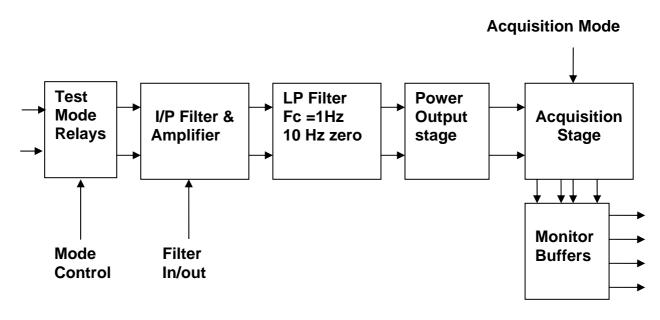

Each PUM Driver board consists of four identical channels and the power regulators which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block has a gain of 1.2.

The third block contains a low pass filter with a corner frequency of 0.5 Hz, followed by a complimentary zero at 5 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 0.5 Hz, the attenuation increases at a rate of 10dB/decade up to the corner frequency of the zero at 5 Hz, after which the characteristic levels off. This filter may be switched in and out by command as required under relay control.

The third block also contains a high pass section which increases the gain at high frequencies to give the required dynamic range at high frequencies.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is wired to have unity gain, the operational amplifier providing the internal gain in the loop. The loop is closed around the buffer/operational amplifier pair. The current limit is set of the driver is set to 0. 5A

The current limit during acquisition is controlled by a circuit which is common to all driver channels (described below).

The outputs are buffered by unity gain voltage followers which drive the monitor board.

## **Acquisition Mode Current Limit**

The current limit during acquisition mode is controlled by an OSEM protection circuit which is common to all channels.

The RMS output currents are measured on the monitor board, then fed into the OSEM Protection Circuit. This circuit is designed to trip if the r.m.s current into an OSEM exceeds the preset limit for more than a predetermined time.

## The OSEM Protection Circuit

The OSEM coils must not be allowed to overheat, as this causes out-gassing. However, during Acquisition, a high current is required for a short period. This period is not long enough to allow the coil to become hot and outgas significantly. However the coils require protection against excessive currents for prolonged periods.

The inputs to the OSEM protection circuit monitor the r.m.s current flowing in each Osem coil. A voltage proportional to the r.m.s current is passed through a delay network. If an OSEM current exceeds the limit by more than a certain time, the threshold level is reached, and the corresponding bistable is set.

The outputs of the four bistables are combined in an OR gated, energising a level shifting circuit which switches off all the drivers. The use of a bistable ensures that oscillation is prevented.

Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......4/1/2010

## 2. Test equipment

Power supplies (At least +/- 20v variable, 1A) Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz)) Digital oscilloscope Analogue oscilloscope Agilent Dynamic Signal Analyser (or similar) Low noise Balanced Driver circuit Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM) | Manufacturer | Model  | Serial Number |

|-----------------|--------------|--------|---------------|

| Scope           | Tektronix    | 2225   |               |

| PSU             | Farnell      | LT30-1 |               |

| PSU             | Farnell      | L30-2  |               |

| Calibrator      | Time         | 1044   |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

Unit......PUM2P......Serial No ..... Test Engineer .....RMC... Date ......4/1/2010

## 3. Inspection

## Workmanship

Inspect the general workmanship standard and comment:

OK

Links: Check that the link W4 is present on each channel.  $\sqrt{}$ Connect the test lead to ground pins 1,3,5 and 7 on P3, the Monitor Input 16 way header.  $\sqrt{}$  Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......4/1/2010

## 4. Continuity Checks

J2

| PIN | SIGNAL | DESCRIPTION   | DESCRIPTION To J1 PIN |              |

|-----|--------|---------------|-----------------------|--------------|

| 1   | PD1P   | Photodiode A+ | 1                     | $\checkmark$ |

| 2   | PD2P   | Photodiode B+ | 2                     | $\checkmark$ |

| 3   | PD3P   | Photodiode C+ | 3                     | $\checkmark$ |

| 4   | PD4P   | Photodiode D+ | 4                     | $\checkmark$ |

|     | 5      | 0V            |                       |              |

| 6   | PD1N   | Photodiode A- | 14                    | $\checkmark$ |

| 7   | PD2N   | Photodiode B- | 15                    | $\checkmark$ |

| 8   | PD3N   | Photodiode C- | 16                    |              |

| 9   | PD4N   | Photodiode D- | 17                    | $\checkmark$ |

## J5

| PIN | SI | GNAL |    | To J1 PIN | OK?          |

|-----|----|------|----|-----------|--------------|

| 1   | Im | on1P |    | 5         | $\checkmark$ |

| 2   | Im | on2P |    | 6         | $\checkmark$ |

| 3   | Im | on3P |    | 7         | $\checkmark$ |

| 4   | Im | on4P |    | 8         | $\checkmark$ |

|     |    | 5    | 0V |           |              |

| 6   | Im | on1N |    | 18        | $\checkmark$ |

| 7   | Im | on2N |    | 19        | $\checkmark$ |

| 8   | Im | on3N |    | 20        | $\checkmark$ |

| 9   | Im | on4N |    | 21        |              |

## Power Supply to Satellite box

J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | $\checkmark$ |

| 10  | V+ (TP1) | +17v Supply | $\checkmark$ |

| 11  | V- (TP2) | -17v Supply | $\checkmark$ |

| 12  | V- (TP2) | -17v Supply | $\checkmark$ |

| 13  | 0V (TP3) |             | $\checkmark$ |

| 22  | 0V (TP3) |             | $\checkmark$ |

| 23  | 0V (TP3) |             | $\checkmark$ |

| 24  | 0V (TP3) |             | $\checkmark$ |

| 25  | 0V (TP3) |             | $\checkmark$ |

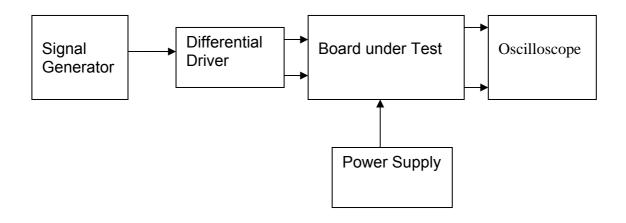

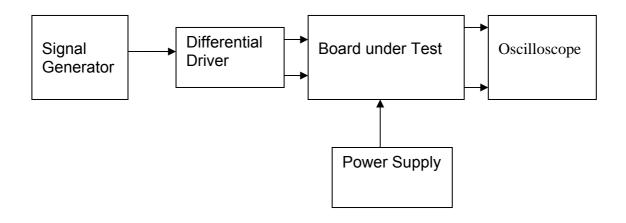

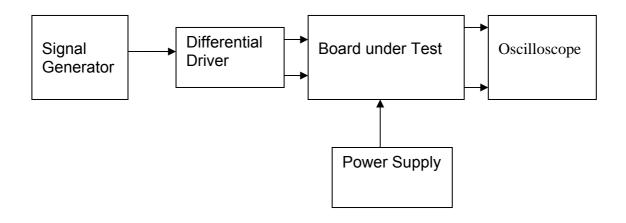

## 5. TEST SET UP

Note:

(1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

(2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

## **Connections:**

#### Differential signal inputs to the board under test:

J3 pins 1, 2, 3, 4 = positive input J3 pins 6, 7, 8, 9 = negative input J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v J1 pin 11,12 = -16.5 J1 pins 22, 23, 24, 25 = 0v

#### **Outputs**

| Ch1+ = J4 pin 1 | Ch1- = J4 pin 9  |

|-----------------|------------------|

| Ch2+ = J4 pin 3 | Ch2- = J4 pin 11 |

| Ch3+ = J4 pin 5 | Ch3- = J4 pin 13 |

| Ch4+ = J4 pin 7 | Ch4- = J4 pin 15 |

Unit......PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......4/1/2010

## 6. Power

# Check that the 3 pin power connector is wired correctly: A1 positive, A2 return, A3 Negative.

Set the power supply outputs to zero.

Connect power to the unit

Ensure that the test ribbon cable is connected to P3, and that pins 1,3,5 and 7 are grounded.

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Press the reset button on the test box.

Record the output voltages, measured on a DVM with 4 or more digits, from each regulator

Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each regulator output.

Record regulator outputs:

| Regulator | Output voltage | Nominal +/-<br>0.5v? | Output noise |

|-----------|----------------|----------------------|--------------|

| +12v TP5  | 12.02v         | $\checkmark$         | 1mV p/p      |

| +15v TP4  | -14.97v        |                      | 1mV p/p      |

| -15v TP6  | -15.08v        |                      | 5mV p/p      |

All Outputs smooth DC, no oscillation? OK

## **Record Power Supply Currents**

| Supply | Current |

|--------|---------|

| +16.5v | 0.49A   |

| -16.5v | 0.3A    |

If the supplies are correct, proceed to the next test.

| UnitPUM2F     | Serial No |

|---------------|-----------|

| Test Engineer | .RMC      |

| Date          | 4/1/2010  |

## 7. Relay Operation

Operate each relay in turn. Observe its operation. LEDs should illuminate when the relays are operated.

#### Filter

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

## **TEST RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

## **ACQUISITION RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

Press the Reset button on the test box. Ensure that the "Not Tripped" indicators are on.

## **NOT TRIPPED indicators**

| Channel | Indicator    |

|---------|--------------|

|         | ON?          |

| Ch1     | $\checkmark$ |

| Ch2     | $\checkmark$ |

| Ch3     | $\checkmark$ |

| Ch4     | $\checkmark$ |

Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......4/1/2010

## 8. Monitor Outputs

Switch out the filters and set the unit to Acquisition Mode.

With a 20 ohm dummy load on each channel, apply a 1v r.m.s input at 100Hz as measured between TP1 and TP2. Measure the voltage monitor outputs and compare with the voltages between TP10 and TP12.

Measure the current monitor outputs and compare with the voltage between the outputs of R29 and R130. Repeat for each channel.

A ribbon cable grounding pins 1, 3, 5 and 7 is necessary in the r.m.s header socket. Press the Reset button on the test box.

Ensure that the "Not Tripped" lights are on.

## 8.1 Voltage Monitors

| Ch. | Output:<br>TP10 to TP12 | Monitor Pins<br>P1 | Monitor<br>Voltage | Pass/Fail:<br>Equal? (+/- 0.1v) |

|-----|-------------------------|--------------------|--------------------|---------------------------------|

| 1   | 1.2V                    | Pin 1 to Pin 2     | 1.2V               | $\checkmark$                    |

| 2   | 1.2V                    | Pin 5 to Pin 6     | 1.2V               | $\checkmark$                    |

| 3   | 1.2V                    | Pin 9 to Pin 10    | 1.2V               | $\checkmark$                    |

| 4   | 1.2V                    | Pin 13 to Pin 14   | 1.2V               | $\checkmark$                    |

## 8.2 Current monitors

| Ch. | Output<br>between R29<br>and R130 | Monitor Pins     | Monitor<br>Voltage | Pass/Fail:<br>Equal? (+/- 0.1v) |

|-----|-----------------------------------|------------------|--------------------|---------------------------------|

| 1   | 1.186V                            | Pin 3 to Pin 4   | 1.186V             | $\checkmark$                    |

| 2   | 1.186V                            | Pin 7 to Pin 8   | 1.186V             | $\checkmark$                    |

| 3   | 1.186V                            | Pin 11 to Pin 12 | 1.186V             | $\checkmark$                    |

| 4   | 1.186V                            | Pin 15 to Pin 16 | 1.186V             |                                 |

Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......5/1/2010

**9.** Frequency Response Test, Low Noise Mode: Insert link W4 for each channel. Switch in the filter and test the response using the signal generator. With a 1Vrms input signal between TP1 and TP2, measure the output between TP10 and TP12. Alternatively, use the Dynamic Signal analyser.

#### 0.1Hz

|     | Output | -6dB   | Simulation  |              | Pass/Fail    |

|-----|--------|--------|-------------|--------------|--------------|

| Ch1 | 7.3dB  | 1.3dB  | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch2 | 7.53dB | 1.53dB | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch3 | 7.46dB | 1.46dB | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch4 | 7.35dB | 1.35dB | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

#### 1Hz

|     | Output | -6dB  | Simulation   |                | Pass/Fail    |

|-----|--------|-------|--------------|----------------|--------------|

| Ch1 | 0.38   | -5.62 | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

| Ch2 | 0.58   | -5.42 | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

| Ch3 | 0.47   | -5.53 | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

| Ch4 | 0.39   | -5.63 | 0.48 to 0.6v | -6.5 to -4.5dB | $\checkmark$ |

#### **10Hz**

|     | Output | -6dB   | Simulation    |                  | Pass/Fail    |

|-----|--------|--------|---------------|------------------|--------------|

| Ch1 | -11.46 | -17.46 | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch2 | -11.47 | -17.47 | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch3 | -11.43 | -17.43 | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

| Ch4 | -11.43 | -17.43 | 0.12 to 0.15v | -16.5 to -18.5dB | $\checkmark$ |

#### 100Hz

|     | Output | -6dB  | Simulation    |                | Pass/Fail    |

|-----|--------|-------|---------------|----------------|--------------|

| Ch1 | -0.4   | -6.4  | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch2 | -0.48  | -6.48 | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch3 | -0.33  | -6.33 | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

| Ch4 | -0.32  | -6.32 | 0.42 to 0.52v | -5.5 to -7.5dB | $\checkmark$ |

#### 1 KHz

|     | Output | -6dB | Simulation   |                | Pass/Fail    |

|-----|--------|------|--------------|----------------|--------------|

| Ch1 | 7.06   | 1.06 | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch2 | 7.3    | 1.3  | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch3 | 7.31   | 1.31 | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

| Ch4 | 7.31   | 1.31 | 1.0 to 1.28v | 0.34 to 2.34dB | $\checkmark$ |

|     | Output | -6dB | Simulation  |              | Pass/Fail    |

|-----|--------|------|-------------|--------------|--------------|

| Ch1 | 7.5    | 1.5  | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch2 | 7.45   | 1.45 | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch3 | 7.49   | 1.49 | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| Ch4 | 7.49   | 1.49 | 1.0 to 1.3v | 0.5 to 2.5dB | $\checkmark$ |

| UnitPUM2P      | Serial No |

|----------------|-----------|

| Test EngineerR | MC        |

| Date5/         | 1/2010    |

**10.** Frequency Response Test, Acquisition Mode: Switch the filter off and Acquisition mode on. Connect a 20 ohm load resistor each channel. Test the response using the signal generator. With a 1v rms input signal between TP1 and TP2, measure the output across the load resistor.

#### 0.1Hz

|     | Output | -6dB  | Sim          | Simulation     |  |

|-----|--------|-------|--------------|----------------|--|

| Ch1 | -39.3  | -45.3 | 0.3 to 0.4mV | -70dB to -65dB |  |

| Ch2 | -39.3  | -45.3 | 0.3 to 0.4mV | -70dB to -65dB |  |

| Ch3 | 38.3   | -44.3 | 0.3 to 0.4mV | -70dB to -65dB |  |

| Ch4 | -39.4  | -45.4 | 0.3 to 0.4mV | -70dB to -65dB |  |

#### 1Hz

|     | Output | -6dB  | Simulation   |                | Pass/Fail |

|-----|--------|-------|--------------|----------------|-----------|

| Ch1 | -37.6  | -43.6 | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch2 | -37.6  | -43.6 | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch3 | -37.6  | -43.6 | 3.3 to 4.2mV | -50dB to -45dB |           |

| Ch4 | -37.5  | -43.5 | 3.3 to 4.2mV | -50dB to -45dB |           |

#### 10Hz

|     | Output | -6dB  | Simulation |                | Pass/Fail    |

|-----|--------|-------|------------|----------------|--------------|

| Ch1 | -22.4  | -28.4 | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch2 | -22.4  | -28.4 | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch3 | -22.4  | -28.4 | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

| Ch4 | -22.3  | -28.3 | 33 to 45mV | -30dB to -27dB | $\checkmark$ |

#### 100Hz

|     | Output | -6dB   | Simulation     |               | Pass/Fail    |

|-----|--------|--------|----------------|---------------|--------------|

| Ch1 | -4.63  | -10.63 | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch2 | -4.63  | -10.63 | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch3 | -4.65  | -10.65 | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

| Ch4 | -4.55  | -10.55 | 0.275 to 0.32V | -12dB to -9dB | $\checkmark$ |

#### 1 KHz

|     | Output | -6dB  | Simulation    |              | Pass/Fail    |

|-----|--------|-------|---------------|--------------|--------------|

| Ch1 | -0.52  | -6.52 | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch2 | -0.52  | -6.52 | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch3 | -0.59  | -6.59 | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch4 | -0.53  | -6.53 | 0.46 to 0.49V | -7dB to -6dB | $\checkmark$ |

|     | Output | -6dB  | Sim           | ulation      | Pass/Fail    |

|-----|--------|-------|---------------|--------------|--------------|

| Ch1 | -0.48  | -6.48 | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch2 | -0.49  | -6.49 | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch3 | -0.55  | -6.55 | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

| Ch4 | -0.49  | -6.49 | 0.47 to 0.49V | -7dB to -6dB | $\checkmark$ |

Unit......PUM2P......Serial No ..... Test Engineer .....RMC... Date ......5/1/2010

## **11. Distortion**

Switch the filters out. Increase input voltage to 10v peak, f = 1KHz. Use 20 Ohm loads. Observe the voltage across each load with an oscilloscope in both Acquisition and Non-Acquisition modes.

|     | Acquisition Mode:<br>Distortion Free? | Non-Acquisition Mo<br>Distortion Free? | ode: |

|-----|---------------------------------------|----------------------------------------|------|

| Ch1 | $\checkmark$                          | $\checkmark$                           |      |

| Ch2 | $\checkmark$                          | $\checkmark$                           |      |

| Ch3 | $\checkmark$                          |                                        |      |

| Ch4 | $\checkmark$                          | $\checkmark$                           |      |

Unit......PUM2P......Serial No ..... Test Engineer .....RMC... Date ......12/5/2010

## **12. Trip Circuit Tests**

A test cable may be used for these tests, consisting of a ribbon cable which plugs into the 16 way header P3. It is convenient to common pins 1, 3, 5, 7, and apply a test voltage to them.

Alternatively an external test box may be used, enabling each input to be tested in turn.

Apply a test voltage to the inputs, and observe the OP400 outputs. An exponential rise in the outputs will be observed. When the logic threshold is reached, the bistable will become set, causing the OR gate output TP25 to go to logic 1. The collector of Q1 will go to high causing the trip pins on each of the drivers to be pulled down to the negative rail, switching them off,

Connect the test lead.

Observe TP25. It should initially be at 0v. If not, turn off all signal inputs and cycle the power supply.

Set the precision voltage source to 1v, representing an r.m.s current of 150mA, and connect it to the ribbon cable input. Observe TP25 for several minutes. It should not go high.

| Stays low? |

|------------|

|------------|

Very slowly increase the voltage, and observe the level at which it trips.

| Trip voltage? | 1.18v |

|---------------|-------|

|---------------|-------|

Reduce the input voltage to 0v, and wait for the capacitors to discharge. Cycle the power supply.

Remove the voltage source, set it to 1.66v representing 250mA. Reconnect it, measuring how long it is before TP25 goes high.

| Time taken to trip? 2. | 2.3 seconds |

|------------------------|-------------|

|------------------------|-------------|

Reduce the input voltage to 0v, and wait for the capacitors to discharge. Cycle the power supply.

Remove the voltage source, set it to 2.66v representing 400mA. Reconnect it, measuring how long it is before TP25 goes high.

| Time taken to trip? 1.4 seconds |  |

|---------------------------------|--|

|---------------------------------|--|

Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date ......5/1/2010

## 12 Load tests

Plug in the 20 Ohm 5W loads. Ensure the links W4 are in place.

## 12.1 Noisy Mode

With the acquisition mode switched out, and filters switched out, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s meter, at the frequencies below.

Calculate the output current in each case (Vout/20).

#### 100Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) |

|-----|----------|------------------|

| Ch1 | 0.234    | 11.7 mA          |

| Ch2 | 0.235    | 11.75 mA         |

| Ch3 | 0.234    | 11.7 mA          |

| Ch4 | 0.234    | 11.7 mA          |

#### 200Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.40     | 20mA             | 16mA          | $\checkmark$ |

| Ch2 | 0.40     | 20mA             | 16mA          | $\checkmark$ |

| Ch3 | 0.40     | 20mA             | 16mA          | $\checkmark$ |

| Ch4 | 0.40     | 20mA             | 16mA          | $\checkmark$ |

#### 1 KHz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.722    | 36.1 mA          | 16mA          | $\checkmark$ |

| Ch2 | 0.723    | 36.1 mA          | 16mA          | $\checkmark$ |

| Ch3 | 0.723    | 36.1 mA          | 16mA          | $\checkmark$ |

| Ch4 | 0.725    | 36.25 mA         | 16mA          | $\checkmark$ |

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.754    | 37.7 mA          | 16mA          | $\checkmark$ |

| Ch2 | 0.754    | 37.7 mA          | 16mA          | $\checkmark$ |

| Ch3 | 0.754    | 37.7 mA          | 16mA          | $\checkmark$ |

| Ch4 | 0.756    | 37.8 mA          | 16mA          | $\checkmark$ |

| UnitPUM2P        | .Serial No |

|------------------|------------|

| Test EngineerRMC |            |

| Date5/1/2010     |            |

#### 12.2 Low noise Mode

With the acquisition mode switched out and filters switched in, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s, at the frequencies below. Calculate the output current in each case (Vout/20).

#### 100Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) |

|-----|----------|------------------|

| Ch1 | 0.089    | 4.45 mA          |

| Ch2 | 0.088    | 4.4 mA           |

| Ch3 | 0.090    | 4.5 mA           |

| Ch4 | 0.090    | 4.5 mA           |

#### 200Hz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.257    | 12.85            | 16mA          | $\checkmark$ |

| Ch2 | 0.257    | 12.57            | 16mA          | $\checkmark$ |

| Ch3 | 0.260    | 13.0             | 16mA          | $\checkmark$ |

| Ch4 | 0.261    | 13.0             | 16mA          | $\checkmark$ |

#### 1 KHz

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.698    | 34.9 mA          | 16mA          | $\checkmark$ |

| Ch2 | 0.702    | 35.1 mA          | 16mA          | $\checkmark$ |

| Ch3 | 0.702    | 35.1 mA          | 16mA          | $\checkmark$ |

| Ch4 | 0.704    | 35.2 mA          | 16mA          | $\checkmark$ |

|     | Vo r.m.s | lo r.m.s (Vo/20) | Specification | Pass/Fail    |

|-----|----------|------------------|---------------|--------------|

| Ch1 | 0.749    | 37.7 mA          | 16mA          | $\checkmark$ |

| Ch2 | 0.753    | 37.6 mA          | 16mA          | $\checkmark$ |

| Ch3 | 0.753    | 37.6 mA          | 16mA          | $\checkmark$ |

| Ch4 | 0.755    | 37.7 mA          | 16mA          | $\checkmark$ |

| UnitPUM2P        | .Serial No |

|------------------|------------|

| Test EngineerRMC |            |

| Date5/1/2010     |            |

### **12.3 Acquisition Mode**

With the acquisition mode switched in, and filters switched out, apply 10v peak at the input to the drive unit. Measure the r.m.s differential voltage across each load resistor in turn using a true r.m.s meter at the frequencies below. Calculate the peak voltages, then the peak output current in each case (Vout/20). Do not leave the board running with a 10v input for long, especially if the heat sink is not fitted.

#### 100Hz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) |

|-----|----------|--------|----------------|

| Ch1 | 4.13     | 5.8    | 292 mA         |

| Ch2 | 4.15     | 5.8    | 293 mA         |

| Ch3 | 4.14     | 5.8    | 292 mA         |

| Ch4 | 4.19     | 5.9    | 296 mA         |

#### 200Hz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail |

|-----|----------|--------|----------------|---------------|-----------|

| Ch1 | 5.45     | 7.7    | 385 mA         | 400mA         |           |

| Ch2 | 5.47     | 7.7    | 386 mA         | 400mA         |           |

| Ch3 | 5.39     | 7.6    | 381 mA         | 400mA         |           |

| Ch4 | 5.53     | 7.8    | 391 mA         | 400mA         |           |

#### 1 KHz

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail |

|-----|----------|--------|----------------|---------------|-----------|

| Ch1 | 5.6      | 7.9    | 396 mA         | 400mA         |           |

| Ch2 | 5.57     | 7.8    | 393 mA         | 400mA         |           |

| Ch3 | 5.55     | 7.8    | 392 mA         | 400mA         |           |

| Ch4 | 5.63     | 7.9    | 398 mA         | 400mA         |           |

|     | Vo r.m.s | Vo pk. | lo pk. (Vo/20) | Specification | Pass/Fail |

|-----|----------|--------|----------------|---------------|-----------|

| Ch1 | 5.66     | 8.00   | 400 mA         | 400mA         |           |

| Ch2 | 5.77     | 8.16   | 400 mA         | 400mA         |           |

| Ch3 | 5.73     | 8.10   | 405 mA         | 400mA         |           |

| Ch4 | 5.74     | 8.11   | 405 mA         | 400mA         |           |

Unit.....PUM2P.....Serial No ..... Test Engineer .....RMC... Date .....13/1/2010

# 13. DC Stability

Use the precision voltage source via a break out box on the input (J3). All filters off. Record the differential output voltage between TP10 and TP12. Check stability while slowly increasing the output voltage. (Link W2 in)

|      | J3 pins<br>1,6 |                    | J3 pins<br>2,7 |                    | J3 pins<br>3,8 |                    | J3 pins<br>4,9 |                    |

|------|----------------|--------------------|----------------|--------------------|----------------|--------------------|----------------|--------------------|

|      | Ch1<br>o/p     | Ch1<br>stable<br>? | Ch2<br>o/p     | Ch2<br>stable<br>? | Ch3 o/p        | Ch3<br>stable<br>? | Ch4<br>o/p     | Ch4<br>stable<br>? |

| -10v | -12.01         | $\checkmark$       | -12.00         | $\checkmark$       | -12.00         | $\checkmark$       | -12.008        | $\checkmark$       |

| -7v  | -8.40          | $\checkmark$       | -8.40          | $\checkmark$       | -8.41          | $\checkmark$       | -8.406         | $\checkmark$       |

| -5v  | -6.00          | $\checkmark$       | -6.10          | $\checkmark$       | -6.00          | $\checkmark$       | -6.004         | $\checkmark$       |

| -1v  | -1.19          | $\checkmark$       | -1.19          | $\checkmark$       | -1.200         | $\checkmark$       | -1.196         | $\checkmark$       |

| 0v   | 0.00           | $\checkmark$       | -0.00          | $\checkmark$       | 0.003          | $\checkmark$       | 0.000          | $\checkmark$       |

| 1v   | 1.19           | $\checkmark$       | 1.19           | $\checkmark$       | 1.200          | $\checkmark$       | 1.198          | $\checkmark$       |

| 5v   | 6.00           | $\checkmark$       | 5.99           | $\checkmark$       | 6.00           | $\checkmark$       | 6.004          | $\checkmark$       |

| 7v   | 8.40           | $\checkmark$       | 8.39           | $\checkmark$       | 8.41           | $\checkmark$       | 8.405          | $\checkmark$       |

| 10v  | 12.00          | $\checkmark$       | 12.00          | $\checkmark$       | 12.00          | $\checkmark$       | 12.007         | $\checkmark$       |

# LIGO Laboratory / LIGO Scientific Collaboration

| LIGO- T0900291                         | Advanced LIGO UK | December 2009 |

|----------------------------------------|------------------|---------------|

| PUM Driver Board Test Report           |                  |               |

| R. M. Cutler, University of Birmingham |                  |               |

Distribution of this document: Inform aligo\_sus

This is an internal working note of the Advanced LIGO Project, prepared by members of the UK team.

Institute for Gravitational Research University of Glasgow Phone +44 (0) 141 330 5884 Fax +44 (0) 141 330 6833 E-mail <u>k.strain@physics.gla.ac.uk</u> Engineering Department CCLRC Rutherford Appleton Laboratory Phone +44 (0) 1235 445 297 Fax +44 (0) 1235 445 843 E-mail J.Greenhalgh@rl.ac.uk School of Physics and Astronomy University of Birmingham Phone +44 (0) 121 414 6447 Fax +44 (0) 121 414 3722 E-mail av@star.sr.bham.ac.uk Department of Physics University of Strathclyde Phone +44 (0) 1411 548 3360 Fax +44 (0) 1411 552 2891 E-mail N.Lockerbie@phys.strath.ac.uk

http://www.ligo.caltech.edu/

http://www.physics.gla.ac.uk/igr/sus/

http://www.sr.bham.ac.uk/research/gravity/rh,d,2.html http://www.eng-external.rl.ac.uk/advligo/papers\_public/ALUK\_Homepage.htm

# Contents

- 1. Description

- 2. Test Equipment

- 3. Inspection

- 4. Continuity Checks

- 5. Test Set Up

- 6. Power

- 7. Relay operation

- 8. Monitor Outputs

- 8.1 Amplifier Monitors

- 8.2 Coil Monitors

- 9. Filter Frequency Response Test

- 10. Distortion

- 11. Trip Circuit tests

- 12 Load Tests 12.1 Noisy Mode 12.2 Low noise Mode 12.3 Acquisition Mode

13. DC Stability

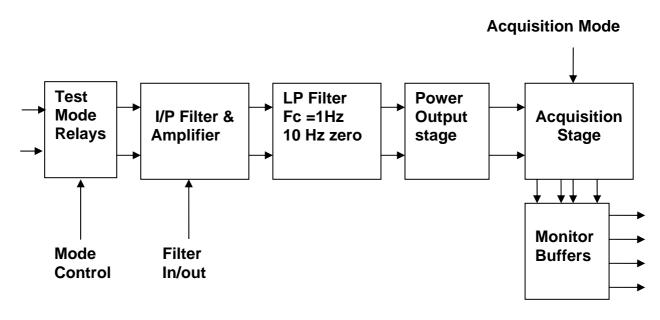

# 1. Description

# **Block diagram**

# Description

Each PUM Driver board consists of four identical channels and the power regulators which provide regulated power to the four channels.

Taking the diagram block by block, the first block contains relays which switch the circuit between the normal inputs and the test inputs.

The second block has a gain of 1.2.

The third block contains a low pass filter with a corner frequency of 0.5 Hz, followed by a complimentary zero at 5 Hz. To a good approximation, the gain is reduced by a factor of 0.7 at 0.5 Hz, the attenuation increases at a rate of 10dB/decade up to the corner frequency of the zero at 5 Hz, after which the characteristic levels off. This filter may be switched in and out by command as required under relay control.

The third block also contains a high pass section which increases the gain at high frequencies to give the required dynamic range at high frequencies.

This is followed by the output buffer stage, consisting of an operational amplifier followed by a power driver buffer. The power driver is wired to have unity gain, the operational amplifier providing the internal gain in the loop. The loop is closed around the buffer/operational amplifier pair. The current limit is set of the driver is set to 0. 5A

The current limit during acquisition is controlled by a circuit which is common to all driver channels (described below).

The outputs are buffered by unity gain voltage followers which drive the monitor board.

# **Acquisition Mode Current Limit**

The current limit during acquisition mode is controlled by an OSEM protection circuit which is common to all channels.

The RMS output currents are measured on the monitor board, then fed into the OSEM Protection Circuit. This circuit is designed to trip if the r.m.s current into an OSEM exceeds the preset limit for more than a predetermined time.

# The OSEM Protection Circuit

The OSEM coils must not be allowed to overheat, as this causes out-gassing. However, during Acquisition, a high current is required for a short period. This period is not long enough to allow the coil to become hot and outgas significantly. However the coils require protection against excessive currents for prolonged periods.

The inputs to the OSEM protection circuit monitor the r.m.s current flowing in each Osem coil. A voltage proportional to the r.m.s current is passed through a delay network. If an OSEM current exceeds the limit by more than a certain time, the threshold level is reached, and the corresponding bistable is set.

The outputs of the four bistables are combined in an OR gated, energising a level shifting circuit which switches off all the drivers. The use of a bistable ensures that oscillation is prevented.

# 2. Test equipment

Power supplies (At least +/- 20v variable, 1A) Signal generator (capable of delivering 10v peak, 0.1Hz to 10 KHz)) Digital oscilloscope Analogue oscilloscope Agilent Dynamic Signal Analyser (or similar) Low noise Balanced Driver circuit Relay test box

Record the Models and serial numbers of the test equipment used below.

| Unit (e.g. DVM) | Manufacturer | Model  | Serial Number |

|-----------------|--------------|--------|---------------|

| Scope           | Tektronix    | 2225   |               |

| PSU             | Farnell      | LT30-1 |               |

| PSU             | Farnell      | L30-2  |               |

| Calibrator      | Time         | 1044   |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

|                 |              |        |               |

# 3. Inspection

### Workmanship

Inspect the general workmanship standard and comment:

Small mark on C2

Links: Check that the link W4 is present on each channel.  $\sqrt{}$ Connect the test lead to ground pins 1,3,5 and 7 on P3, the Monitor Input 16 way header. $\sqrt{}$

# 4. Continuity Checks

J2

| PIN | SIGNAL | DESCRIPTION   | To J1 PIN | OK?          |

|-----|--------|---------------|-----------|--------------|

| 1   | PD1P   | Photodiode A+ | 1         | $\checkmark$ |

| 2   | PD2P   | Photodiode B+ | 2         | $\checkmark$ |

| 3   | PD3P   | Photodiode C+ | 3         | $\checkmark$ |

| 4   | PD4P   | Photodiode D+ | 4         | $\checkmark$ |

| 5   | 0V     | $\checkmark$  |           |              |

| 6   | PD1N   | Photodiode A- | 14        | $\checkmark$ |

| 7   | PD2N   | Photodiode B- | 15        | $\checkmark$ |

| 8   | PD3N   | Photodiode C- | 16        |              |

| 9   | PD4N   | Photodiode D- | 17        |              |

# J5

| PIN | SIGNAL |              | To J1 PIN | OK?          |

|-----|--------|--------------|-----------|--------------|

| 1   | Imon1P |              | 5         | $\checkmark$ |

| 2   | Imon2P |              | 6         | $\checkmark$ |

| 3   | Imon3P |              | 7         | $\checkmark$ |

| 4   | Imon4P |              | 8         | $\checkmark$ |

| 5   | 0V     | $\checkmark$ |           |              |

| 6   | Imon1N |              | 18        | $\checkmark$ |

| 7   | Imon2N |              | 19        | $\checkmark$ |

| 8   | Imon3N |              | 20        | $\checkmark$ |

| 9   | Imon4N |              | 21        | $\checkmark$ |

# Power Supply to Satellite box

J1

| PIN | SIGNAL   | DESCRIPTION | OK?          |

|-----|----------|-------------|--------------|

| 9   | V+ (TP1) | +17v Supply | $\checkmark$ |

| 10  | V+ (TP1) | +17v Supply | $\checkmark$ |

| 11  | V- (TP2) | -17v Supply | $\checkmark$ |

| 12  | V- (TP2) | -17v Supply | $\checkmark$ |

| 13  | 0V (TP3) |             | $\checkmark$ |

| 22  | 0V (TP3) |             | $\checkmark$ |

| 23  | 0V (TP3) |             | $\checkmark$ |

| 24  | 0V (TP3) |             | $\checkmark$ |

| 25  | 0V (TP3) |             | $\checkmark$ |

# 5. TEST SET UP

Note:

(1) Input signal to differential amplifier is generally stated in the tests below. There is therefore an inherent gain of 2 in the system.

(2) Some signal generators will indicate 1vpk/pk when the output is in fact 1v Peak into the high impedance Differential driver used. The test procedure refers to the actual voltage out of the signal generator.

# **Connections:**

#### Differential signal inputs to the board under test:

J3 pins 1, 2, 3, 4 = positive input J3 pins 6, 7, 8, 9 = negative input J3 pin 5 = ground

#### Power

J1 pin 9, 10 = +16.5v J1 pin 11,12 = -16.5 J1 pins 22, 23, 24, 25 = 0v

#### **Outputs**

| Ch1+ = J4 pin 1 | Ch1- = J4 pin 9  |

|-----------------|------------------|

| Ch2+ = J4 pin 3 | Ch2- = J4 pin 11 |

| Ch3+ = J4 pin 5 | Ch3- = J4 pin 13 |

| Ch4+ = J4 pin 7 | Ch4- = J4 pin 15 |

# 6. Power

# Check that the 3 pin power connector is wired correctly: A1 positive, A2 return, A3 Negative.

Set the power supply outputs to zero.

Connect power to the unit

Ensure that the test ribbon cable is connected to P3, and that pins 1,3,5 and 7 are grounded.

Increase the voltages on the supplies to +/-3V.

Determine that the supply polarities are correct on TP1 and TP2.

If they are, increase input voltages to +/- 16.5v.

Press the reset button on the test box.

Record the output voltages, measured on a DVM with 4 or more digits, from each regulator

Observe the output on an analogue oscilloscope, set to AC. Measure and record the peak to peak noise on each regulator output.

Record regulator outputs:

| Regulator | Output voltage | Nominal +/-<br>0.5v? | Output noise |

|-----------|----------------|----------------------|--------------|

| +12v TP5  | 12.04          | $\checkmark$         | 5 mV pk/pk   |

| +15v TP4  | 14.95          | $\checkmark$         | 5mV          |

| -15v TP6  | -14.95         | $\checkmark$         | 25 mV        |

| All Outputs smooth DC, no oscillation? |                      |

|----------------------------------------|----------------------|

|                                        | interference spike - |

|                                        | probably pick up.    |

# **Record Power Supply Currents**

| Supply | Current |

|--------|---------|

| +16.5v | 0.3A    |

| -16.5v | 0.25A   |

If the supplies are correct, proceed to the next test.

# 7. Relay Operation

Operate each relay in turn.

Observe its operation. LEDs should illuminate when the relays are operated.

# Filter

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

#### **TEST RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

# **ACQUISITION RELAYS**

| Channel | Indicator    |              | OK?          |

|---------|--------------|--------------|--------------|

|         | ON           | OFF          |              |

| Ch1     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch2     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch3     | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Ch4     | $\checkmark$ |              |              |

Press the Reset button on the test box. Ensure that the "Not Tripped" indicators are on.

# **NOT TRIPPED indicators**

| Channel | Indicator    |

|---------|--------------|

|         | ON?          |

| Ch1     | $\checkmark$ |

| Ch2     | $\checkmark$ |

| Ch3     | $\checkmark$ |

| Ch4     | $\checkmark$ |

# 8. Monitor Outputs

Switch out the filters and set the unit to Acquisition Mode.

With a 20 ohm dummy load on each channel, apply a 1v r.m.s input at 100Hz as measured between TP1 and TP2. Measure the voltage monitor outputs and compare with the voltages between TP10 and TP12.

Measure the current monitor outputs and compare with the voltage between the outputs of R29 and R130. Repeat for each channel.

A ribbon cable grounding pins 1, 3, 5 and 7 is necessary in the r.m.s header socket. Press the Reset button on the test box.

Ensure that the "Not Tripped" lights are on.

#### **Monitor Pins** Pass/Fail: Ch. Output: Monitor TP10 to TP12 **P1** Voltage Equal? (+/- 0.1v) 1 1.2v Pin 1 to Pin 2 1.2v $\checkmark$ 2 $\sqrt{}$ 1.2v Pin 5 to Pin 6 1.2v $\sqrt{}$ 3 Pin 9 to Pin 10 1.2v 1.2v $\sqrt{}$ 4 Pin 13 to Pin 14 1.2v 1.2v

#### 8.1 Voltage Monitors

# 8.2 Current monitors

| Ch. | Output<br>between R29<br>and R130 | Monitor Pins     | Monitor<br>Voltage | Pass/Fail:<br>Equal? (+/- 0.1v) |

|-----|-----------------------------------|------------------|--------------------|---------------------------------|

| 1   | 1.188v                            | Pin 3 to Pin 4   | 1.188v             | $\checkmark$                    |

| 2   | 1.188v                            | Pin 7 to Pin 8   | 1.188v             | $\checkmark$                    |

| 3   | 1.188v                            | Pin 11 to Pin 12 | 1.188v             | $\checkmark$                    |

| 4   | 1.188v                            | Pin 15 to Pin 16 | 1.188v             | $\checkmark$                    |

**9.** Frequency Response Test, Low Noise Mode: Insert link W4 for each channel. Switch in the filter and test the response using the signal generator. With a 1Vrms input signal between TP1 and TP2, measure the output between TP10 and TP12. Alternatively, use the Dynamic Signal analyser.

#### 0.1Hz

|     | Output | -6dB | Simulation  |              | Pass/Fail    |

|-----|--------|------|-------------|--------------|--------------|

| Ch1 | 1.2v   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch2 | 1.2v   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch3 | 1.2v   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

| Ch4 | 1.2v   |      | 1.0 to 1.3v | 0.4 to 2.4dB | $\checkmark$ |

#### 1Hz